Digital Object Identifier 10.1109/ACCESS.2021.3104741

# Wideband OFDM-based Communications in Bus Topology as a Key Enabler for Industry 4.0 Networks

## JORGE LUIS GONZÁLEZ RIOS<sup>1</sup>, JORGE TORRES GÓMEZ<sup>2</sup>, (Member, IEEE), RAJESH KUMAR SHARMA<sup>3</sup>, (Member, IEEE), FALKO DRESSLER<sup>4</sup>, (Fellow, IEEE), and M. JULIA FERNÁNDEZ-GETINO GARCÍA<sup>5</sup>, (Member, IEEE)

<sup>1</sup>Interdisciplinary Centre for Security, Reliability and Trust (SnT), University of Luxembourg, L-1855, Luxembourg (email: jorge.gonzalez@uni.lu) <sup>2</sup>School of Electrical Engineering and Computer Science, TU Berlin, Germany (e-mail: torres-gomez@ccs-labs.org)

<sup>3</sup>Department of Digital Signal Processing and Circuit Technology, Chemnitz University of Technology, 09126, Chemnitz, Germany (email: rajesh-kumar.sharma@etit.tu-chemnitz.de)

<sup>4</sup>School of Electrical Engineering and Computer Science, TU Berlin, Germany (e-mail: dressler@ccs-labs.org)

<sup>5</sup>Department of Signal Theory and Communications, Carlos III University of Madrid, 28911, Leganés, Madrid, Spain (e-mail: mjulia@tsc.uc3m.es)

Corresponding author: Jorge Luis González Rios (e-mail: jorge.gonzalez@uni.lu).

This work is part of the Elektromobilität mit Redundanter Intelligenter Kommunikations-Architektur (ERIKA) Project, supported by the Bundesministerium für Wirtschaft und Energie, Germany. It has been supported in part by the Spanish National Project TERESA-ADA (TEC2017-90093-C3-2-R) funded by (MINECO/AEI/FEDER, UE). This research has been also supported in part by the CORE project COHESAT funded by the Fond National de la Recherche (FNR), Luxembourg.

**ABSTRACT** The Industry 4.0 paradigm conceives a cyber-physical supporting framework for the manufacturing processes in smart factories. In this context, solutions concerning the wired communications at the field-level have been reported which utilize either fieldbuses, which exhibit a huge distance range but a reduced data rate in a bus topology, or Ethernet-based technologies, which provide an increased data rate but reduced distance in a ring topology. To overcome this shortage, we propose the use of orthogonal frequency division multiplexing (OFDM) to significantly increase the achievable data rates over large distances in industrial bus systems. Also, we establish a novel methodology to compute the signal-tonoise ratio between arbitrary pairs of nodes, which in turn allows to compute the communication capacity. Our wideband system was validated by connecting up to 32 nodes in the distance range 100 m–1 km. Compared to fieldbuses, the results of the proposal exhibit an amazing improvement in data rate of about fifty times for 100 m distance and more than ten times for 0.5 km. Moreover, with respect to Ethernet-based solutions, the results show a relevant improvement in the data rate of around five times for 100 m distance, but Ethernet-based systems cannot go beyond this distance, to which our proposal is not limited.

**INDEX TERMS** Wideband, OFDM, Circuit Noise, Circuit Analysis, Field buses, Industry 4.0, System Analysis and Design.

#### I. INTRODUCTION

THE new Industry 4.0 paradigm aims to implement intelligent networks to integrate the human workers and machines supporting the future smart factories [1], [2]. The development of the underlying network technologies has been a main focus of attention since the early days of Industry 4.0, when the German government defined a high-tech strategy [3]. In this direction, the implementation of production systems for the integration of computing, communication, and control – thus, resulting in so-called Cyber-Physical Production Systems – plays a major role to support the integration of machines, sensors, and management systems in smart factories [4]. We concentrate on the digital communication infrastructure, which is supposed to provide wideband network connection as a key enabler for this process.

Typically, three types of communication systems are deployed for industrial applications [5]: fieldbuses, industrial Ethernet, and industrial wireless networks. On one hand, the Fieldbuses and Ethernet-based networks connect field nodes such as sensors, actuators, and controllers through a wired bus, as depicted in Fig. 1 for the one-level architecture [6]. On the other hand, wireless solutions have also been deployed provided their flexibility and low costs [7] (even with

Figure 1: Fieldbus network for industrial applications.

the 5th generation wireless communication systems (5G) technology [8]), however, wired networks are still preferred for industrial applications due to their higher reliability [9].

Nowadays, the deployed techonolgies relying on the fieldbus protocols (e.g., PROFIBUS, FIP, WorldFIP) guarantee the timing constraints of industrial applications in order to support strict determinism and fast reaction times [10]. Classical fieldbus solutions reach long distances of connections (up to 1 km) but are known for low bandwidth transmissions and can not generally support the transmission of high data rates of 100 Mbit/s and beyond [11]. Thus, fieldbuses are mainly deployed for low-speed communication (human control) and programmable logic controller functions (process control).

To support higher data rates, Ethernet is considered as an alternative solution [12]. It is easy to deploy, adapters are cheap, it is widely accepted, and the offered high data rates (>100 Mbit/s) are strongly demanded. However, these solutions are limited by the maximum distance of connections between nodes of 100 m [13]. Besides, costs are still high in comparison to fieldbuses (mainly due to the need of Ethernet switches on each fieldbus component).

To overcome these limitations on the industrial communications' scenario, novel solutions that attain both, long distance of connections and high data rates, should be explored. It is envisaged that higher data-rate communications can be achieved on fieldbuses by addressing wideband multicarrier waveforms in contrast to the narrowband signals used in classical fieldbuses. In specifics, multicarrier waveforms, like orthogonal frequency division multiplexing (OFDM), can be transmitted over the large distances covered by fieldbuses. This becomes rather useful to interconnect assembly lines along several facilities, then to avoid the limited range of Ethernet-based solutions.

OFDM waveforms on fieldbuses will introduce several advantages. For instance, the use of bit-loading algorithms will avoid those frequency bands where strong interference is observed [14]. Access mechanisms (by means of orthogonal frequency division multiple access (OFDMA) [15]) will not only avoid the user's collisions on the bus, but will allocate available resources (in time and frequency) in accordance with required node's quality of service (QoS) metrics. Also, multicarrier communication is a mature technology to deploy wideband communication services over cable. This is, for example, the case of digital subscriber lines (DSL) [16], home networking (G.hn) [17], and power line communications (PLC) [18] – all these technologies make use of OFDM transceivers. However, the extension to wired fieldbus systems has not yet been addressed in spite of its potential to provide higher datarates for long distances.

Since the use of OFDM in the fieldbus has not been reported yet, its achievable bit rate is still unknown in this communication scenario. Its obtaining is a challenge considering the impact of the corresponding hardware impairments and noises, produced by the variety of connected nodes. Its derivation, in terms of the signal-to-noise ratio (SNR) metric, can be further elaborated to overcome the limitation of well-established techniques for the analysis of cascaded stages [19], and the complexity of methods reported for multiport networks [20]–[23].

In this paper, we design and analyze the physical layer to implement an OFDM-based fieldbus. We specifically consider the capabilities of the use of OFDM waveforms to transmit higher data rates over high distances. We develop an analytical methodology in order to compute the channel capacity, and we illustrate its application considering real circuit devices and transmission medium characteristics.

Our main contributions can be summarized as follows:

- A fieldbus communication system is designed (from the physical layer perspective) to support the transmission of OFDM waveforms in a bus topology.

- A methodology to compute the perceived SNR between nodes is elaborated to account for the achievable bit rate, which overcomes the distributed nature of multiple noisy transmitting devices in the bus.

- Metrics for the network dimensioning are provided regarding the total number of nodes and the bus length.

The rest of the paper is organized as follows. Relevant technologies for fieldbuses and industrial Ethernet are summarized and discussed in Section II. Then, Section III introduces the proposed design for the OFDM-based fieldbus system with enhanced transmission rate capabilities. Section IV presents a methodology to compute the perceived SNR between nodes' pairs, that will allow the calculation of the achievable bit rate. This proposed methodology is validated in Section V, by comparing the results with those obtained through a circuit simulator and considering commercially available devices. Finally, we present and discuss performance results regarding the evaluation of the channel capacity in Section VI followed by some concluding remarks in Section VII.

## II. REVIEW OF FIELD-LEVEL COMMUNICATION TECHNOLOGIES

Fieldbuses and Ethernet-based solutions are currently specified by the IEC 61158 standard [24] with 26 different communications profiles defined in the IEC 61784 parts 1 and 2 [25], [26]. In this section, we provide a comparative

|                | Connector<br>Interface | Standard                                                                             | Transmission<br>Speed                  | Distance<br>(up to)                                               | Total number<br>of nodes (max) | Topology         | Cable                      |

|----------------|------------------------|--------------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------|--------------------------------|------------------|----------------------------|

| Fieldbuses     | RS 485                 | PROFIBUS                                                                             | 9.6 kbit/s $\sim 12$ Mbit/s            | 1.2 km                                                            | 32                             | Bus              | Twisted-pair*              |

|                |                        | H1 Foundation Fieldbus                                                               | 31.25 kbit/s                           | 1.9 km                                                            | 32                             | Bus              |                            |

|                |                        | P-NET                                                                                | 76.8 kbit/s                            | 600 m<br>1.2 km                                                   | 127                            | Bus<br>Ring      |                            |

|                |                        | INTERBUS                                                                             | 500 kbit/s $\sim 2$ Mbit/s             | $400\mathrm{m}^a$                                                 | 64                             | Ring             |                            |

|                | RS 422                 | CIP-ControlNet                                                                       | 5 Mbit/s                               | 1 km<br>500 m                                                     | 2<br>48                        | Bus              | Coaxial $75\Omega$         |

|                | CAN Interface          | CAN, CIP-DeviceNet                                                                   | 125 kbps<br>250 kbit/s<br>500 kbit/s   | $500 \text{ m}^{b}$<br>$250 \text{ m}^{b}$<br>$100 \text{ m}^{b}$ | 64                             | Bus              | Thick, thin, or flat       |

|                | FIELDRIVE              | WorldFIP                                                                             | 31.25 kbit/s<br>1 Mbit/s<br>2.5 Mbit/s | 10 km<br>1 km<br>700 m                                            | 64                             | Bus<br>Star      | Twisted-pair*              |

|                | RS 232                 | P-NET                                                                                | 230.4 kbps                             | 20 m <sup>a</sup>                                                 | 2                              |                  | -                          |

| Ethernet-based | BNC                    | HSE Foundation Fieldbus<br>Ethernet/IP, Modbus/TCP,<br>Modbus RTPS, TSN, TTE         | 10 Mbit/s                              | 185 m <sup>a</sup>                                                | 32 <sup>c</sup>                | Bus              | Coaxial <sup>f</sup>       |

|                | RJ 45                  | PROFINET IO, PROFINET CBA,<br>PROFINET SRT, EtheReal<br>P-NET on IP, TCnet, EtherCAT | 100 Mbit/s                             | 100 m <sup>a</sup>                                                | $100^{d}$                      | Ring<br>Switched | Twisted-pair <sup>g*</sup> |

Table 1: Summary of transmission technologies for the fieldbus and Ethernet-based solutions (derived from [10]).

The quantities in this table are given without the use of repeaters. <sup>a</sup>Referred to point-to-point link regarding the ring topology; <sup>b</sup>Referred to the thick cable, distances regarding the thin and flat cables are provided in [10]; <sup>c</sup>Reported by the HSE Foundation Fieldbus; <sup>d</sup>Reported for one segment in P-NET on IP, also reported achieving a cycle time of 0.1 ms in EtherCAT [27]; <sup>f</sup>Referred to 10BASE2 IEEE standard; <sup>g</sup>Referred to 100BASET IEEE standard. \*Shielded twisted-pair is specified to be used by PROFIBUS, P-NET, and WorldFIP.

summary regarding the specifications on the PHY layer considering the transmission technologies, wired medium, topologies, achievable speed, and the total number of connected nodes.

Table 1 summarizes the main parameters for the existing fieldbus and Ethernet networks. Several reported connector interfaces and cable types are employed to interconnect nodes for a variety of topologies. Regarding the bus topology, and outperforming Ethernet, the PROFIBUS fieldbus, exhibits the best balance between the transmission speed, achievable distance, and total number of nodes without the use of repeaters. In the case of a ring topology, the Ethernetbased solutions provide the best balance to interconnect the nodes.

To fulfill the real-time guarantees of the field-level, the Ethernet-based solutions address strategies to suppress collisions or solve them in a deterministic manner [27]. Some solutions are compatible with pure Ethernet nodes. This is the case for protocols running on top of TCP/UDP/IP, often following the published-subscribe model on the application layer (Ethernet/IP, Modbus/TCP, Modbus RTPS, PROFINET CBA, PROFINET IO). Other Ethernet-compatible solutions implement traffic smoothing and shaping, or resource reservation on switches (PROFINET SRT, EtheReal). Finally, modified-Ethernet solutions can only be deployed when all the nodes have been adapted accordingly. This is the case of P-NET on IP, TCnet, and EtherCAT – which deploy toking passing mechanisms –, or EPA and VNET/IP – which implement polling cycles by a master node or using time division multiplex access (TDMA) schemes with distributed medium access–, or PROFINET IRT, time-triggered ethernet (TTE) and time sensitive networks (TSN) – which implement synchronization protocols on switches to guarantee end-to-end restriction delays over switched topologies [1], [28].

In general, fieldbuses are supposed to provide efficient transmissions by using short data messages and reduced computational capabilities on nodes. This conception is today a major impediment for industrial applications where multimedia information processing is incorporated. On the other hand, although Ethernet-based solutions support data streaming transmissions, their adaptation to the field-level of industrial environments can be further improved with new physical layer designs. Specifically, when implementing OFDM transceivers, in contrast to binary signaling (Ethernet and fieldbuses), their benefits regarding the flexible waveform, numerology, and frame parameters design [29] may account for optimized resource allocation schedulers adjusted to the channel condition.

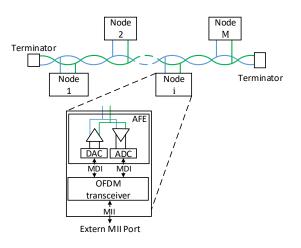

Figure 2: Simplified diagram of the circuit interface in the bus topology.

### **III. PROPOSED FIELDBUS COMMUNICATION NETWORK**

The aim of this proposed design is to devise a fieldbus solution of high transmission capacity (>100 Mbit/s) and high distance (up to 1 km) to interconnect sensors and actuators with higher flexibility than the counterpart Ethernet-based solutions. Flexibility is referred to avoid the upper limit distance to interconnect a pair of nodes (100 m) imposed by the ring topology according to Ethernet-based solutions. In our proposal, the bus will be comprised of a twisted-pair cable, where nodes (controller, sensors, and actuators) will be connected through a bus topology as depicted in Fig. 2. This is a simple electrical bus where all nodes are able to transmit and receive simultaneously as long as collisions are avoided.

Here, we focus on the physical layer of the connected node. It will be comprised of the communication module (OFDM transceiver) and the analog-front-end (AFE) circuit. The higher layers, i.e., link layer and above, will be connected through the media-independent interface (MII) port in Fig. 2. The OFDM transceiver will embody the digital circuit to synchronize and implement the direct and inverse fast-Fourier-transform (FFT) to properly transmit and receive the OFDM waveform through the mediumdependent interface (MDI). The AFE will be comprised of an analog-to-digital converter (ADC), a digital-to-analog converter (DAC), and amplifiers to interface the bus.

The system under consideration is comprised of M nodes. Each node is able to transmit and receive OFDM waveforms of given parameters (FFT/IFFT-size denoted by NFFT and subcarrier spacing denoted by  $\Delta f$ ). Multiple access to the channel will be supported by OFDMA, where a scheduler mechanism will allocate users per available orthogonal resources (resource blocks) to avoid collisions. All introduced delays have a deterministic nature.

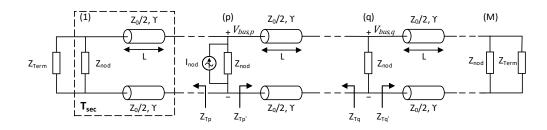

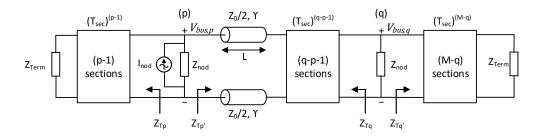

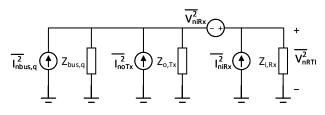

The scheme in Fig. 3 depicts the equivalent circuit repre-

sentation of the connection between nodes. The twisted-pair cable is analyzed in terms of its characteristic impedance,  $Z_0$ , and the propagation factor,  $\gamma$ . Nodes are equally spaced between each other by a cable length of L meters, and they are represented by the impedance  $Z_{nod}$ . Load terminators are connected to each end of the bus line, given by  $Z_{Term}$ . Ideally, with  $Z_{Term} = Z_0$  and  $Z_{nod} \gg Z_0$  the bus will exhibit the same impedance to every node, according to the transmission line theory [30].

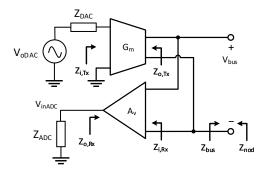

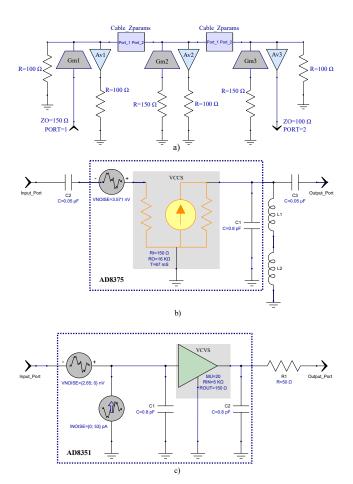

For the ease of representation, only one signal source is represented, as shown in Fig. 3, to illustrate the communication link between an arbitrary pair of transmitterreceiver (Tx-Rx) p-th and q-th nodes, respectively. However, all the nodes have the capability of transmitting and receiving simultaneously through the circuit diagram depicted in Fig. 4. In this diagram, each node is conceived by the connections of the following basic elements: DAC, ADC, a transconductance amplifier as the transmitter, and a voltage amplifier as the receiver. These classes of amplifier were selected as they offer a high impedance to the bus (i.e. the output impedance of the transmitter and the input of the receiver). The objective of this decision is to avoid loading effects, with respect to each other and to the bus. The generated OFDM waveform will be provided by the DAC circuit (modeled here by the source  $V_{oDAC}$  and the impedance  $Z_{DAC}$ ), and the received OFDM waveform will be transformed to the digital domain by the ADC circuit (modeled here by the impedance  $Z_{ADC}$ ).

### **IV. METHODOLOGY TO EVALUATE THE SNR**

In the following, we illustrate the methodology to compute the perceived SNR on a link between an arbitrary pair of transmitter-receiver nodes, denoted by p and q, respectively, as depicted in Fig. 3. Considering the transmission of conventional OFDM waveforms (without pre-filtering techniques) [31], the perceived SNR per m-th subcarrier will be given by the ratio

$$SNR_{m} = \frac{\int_{f_{m}-\frac{\Delta f}{2}}^{f_{m}+\frac{\Delta f}{2}} |H(f)|^{2} \cdot \frac{A_{c}^{2}}{\Delta f/2} \operatorname{sinc}^{2}\left(\frac{f-f_{m}}{\Delta f/2}\right) \mathrm{d}f}{\int_{f_{m}-\frac{\Delta f}{2}}^{f_{m}+\frac{\Delta f}{2}} [N_{om}(f) + N_{e} + |H(f)|^{2} \cdot N_{e}] \,\mathrm{d}f},$$

(1)

computed in the frequency domain through the Rayleigh's theorem [32]. The numerator and denominator account for the received power for signal and noise, respectively. In the case of the numerator, the received power is represented through the bus transfer function H(f) times the signal power density – represented by the sinc(·) function after using the Fourier transform pair for a time-limited sine wave of amplitude  $A_c$  and duration  $\frac{2}{\Delta f}$ .

The bus transfer function, from the DAC output (in the transmitter at p-th node) to the ADC input (in the receiver at q-th node), is given by

$$H(f) = \frac{G_{\text{Tx}} \cdot G_{\text{Rx}}}{L_{\text{pq}}}(f), \qquad (2)$$

VOLUME 9, 2016

Figure 3: System model of the connected nodes.

Figure 4: System model of the transmitting and receiving structure on each node.

where,  $L_{pq}(f) = \frac{V_{bus,p}}{V_{bus,q}}(f)$  denotes the voltage attenuation from the output of the transmitting amplifier (*p*-th node) to the input of the receiving amplifier (*q*-th node),  $G_{Tx} = \frac{V_{bus,p}}{V_{oDAC}}$ , and  $G_{Rx} = \frac{V_{inADC}}{V_{bus,q}}$  denote the voltage gain of the transmitter and receiver amplifying stages, respectively. Besides, *m* is the subcarrier index,  $A_c$  is the subcarrier amplitude at the DAC output, *f* is the frequency, and  $\Delta f$  is the bandwidth of the given subcarrier (given by the OFDMwaveform subcarrier spacing).

In the case of the denominator in (1), the total noise will account for the superposition of the variety of sources:  $N_{om}$  is the noise spectral density (mean-square voltage) introduced by the amplifiers and the passive elements (thermal noise),  $N_e$  will account for the quantization noise errors introduced by the ADC circuit, and the term  $|H(f)|^2 \cdot N_e$  will account for the perceived noise at the receiver side regarding the DAC transmitter circuit. Here we consider  $N_e = \frac{1}{12} \frac{A_e^2}{2^{2(n-1)}}$  with n as the total number of bits [33]. For simplicity, we assume that same total number of bits are used by the DAC and ADC circuits.

Based on the relations in (1), the communication performance will be mainly governed by three main factors: the bus transfer function between nodes (given by H(f) in (2)), the effect of the thermal noise (considered by  $N_{om}(f)$ ), and the quantization noise errors (considered by  $N_e$ ). The impact of the quantization noise error is directly computed by the relation with the total number of bits (as presented on the previous paragraph). However,  $L_{pq}(f)$  in (2) and  $N_{om}(f)$  in (1) must be computed considering the location of the *p*-th and *q*-th nodes. The proper analytical expressions regarding these terms will be derived in the next subsections.

## A. OBTAINING THE BUS TRANSFER FUNCTION BETWEEN ARBITRARY PAIRS OF NODES

The bus transfer function (given by H(f) in (2)) takes into account all the elements between the DAC output (in the transmitter at *p*-th node) and the ADC input (in the receiver at *q*-th node): the amplifiers (transmitter and receiver), the twisted pair cable segment between *p* and *q*, as well as the loading effects of the bus tails ( $Z_{Tp}$  and  $Z_{Tq'}$ ), as represented in Fig. 3. For brevity, here we omit the dependence of the obtained quantities from the variable *f*.

#### 1) Computing the numerator of the bus transfer function

The numerator of the bus transfer function in (2) comprises the gains of the amplifiers at the transmitter and receiver nodes. Considering the connections in Fig. 4, these two voltage gains can be computed as

$$G_{\mathrm{Tx,p}} = G_m \left( Z_{\mathrm{nod}} || Z_{\mathrm{bus,p}} \right) \frac{Z_{i,\mathrm{Tx}}}{Z_{i,\mathrm{Tx}} + Z_{\mathrm{DAC}}},\tag{3}$$

and

$$G_{\mathrm{Rx},\mathrm{q}} = A_v \frac{Z_{\mathrm{ADC}}}{Z_{\mathrm{ADC}} + Z_{o,\mathrm{Rx}}},\tag{4}$$

respectively, where  $G_m$  is the transconductance of the transmitter amplifier with shorted output and  $Z_{i,Tx}$  is its input impedance,  $Z_{DAC}$  is the output impedance of the DAC circuit,  $Z_{nod}$  is the impedance seen into the node from the bus, given by  $Z_{nod} = Z_{o,Tx} ||Z_{i,Rx}$  (considering the connections in Fig. 4),  $Z_{bus,p}$  is the impedance seen into the bus from *p*-th node,  $A_v$  is the voltage gain of the unloaded receiver amplifier,  $Z_{o,Rx}$  is its output impedance and  $Z_{ADC}$  is the input impedance of the ADC circuit. The operator || is used to denote the calculation of the equivalent impedance of parallel connected elements.

Based on the relations in (3) and (4), only the term  $Z_{bus,p}$  will be dependent on the position of the node in the bus, while the remaining terms will be directly defined by the specific circuit parameters (ADC, DAC, and the amplifiers).

Figure 5: System model of the transmitting and receiving structure on each node.

To compute the bus impedance  $Z_{bus,p}$ , we model the system as the cascade connection of identical two-ports networks, the elements of which are represented inside the dottedline box in Fig. 3. Considering the connection of the node impedance  $Z_{nod}$  and a cable segment of L meters, the corresponding T-matrix will be given by

$$T_{\rm sec} = \begin{bmatrix} 1 & 0\\ Y_{\rm nod} & 1 \end{bmatrix} \cdot T_{\rm cable},\tag{5}$$

where  $Y_{\text{nod}} = Z_{\text{nod}}^{-1}$  is the node's output admittance, and the *T*-parameters of the cable are [34]

$$T_{\text{cable}} = \begin{bmatrix} \cosh\left(\gamma L\right) & Z_0 \sinh\left(\gamma L\right) \\ Z_0^{-1} \sinh\left(\gamma L\right) & \cosh\left(\gamma L\right) \end{bmatrix}.$$

(6)

Then, the *T*-matrix for any arbitrary number of consecutive *n* sections can be found as the *n*-th power of  $T_{sec}$ , and the system can be modeled as depicted in Fig. 5. Next, from the *T*-matrix equations [35], we obtain the equivalent impedance to the left side of *p*, denoted by  $Z_{Tp}$ , as

$$Z_{\rm Tp} = \frac{t_{12} + t_{22} \cdot Z_{\rm Term}}{t_{11} + t_{21} \cdot Z_{\rm Term}},\tag{7}$$

by considering  $Z_{\text{Tp}}$  as the output impedance of the network and  $Z_{\text{Term}}$  the load connected in the input, where  $t_{ij}$  are the *T*-parameters regarding the matrix  $T_{sec}^{(p-1)}$ .

Due to the symmetry of the network, the equivalent impedance to the right side of the *p*-th node, denoted by  $Z_{\text{Tp}'}$  in Figures 3 and 5, is the same as the equivalent to the left of a node located at the position p' = M - p + 1. Accordingly,  $Z_{\text{Tp}'}$  can also be found by using (7), but considering the parameters from the matrix  $T_{sec}^{(M-p)}$ . After obtaining  $Z_{\text{Tp}}$  and  $Z_{\text{Tp}'}$ , the impedance seen into the bus from *p*-th node will be  $Z_{\text{bus,p}} = Z_{\text{Tp}} ||Z_{\text{Tp}'}$ . By a similar procedure, the impedance terms related to any node can be calculated.

For the particular case of  $Y_{\text{nod}} = 0$  (i.e.  $Z_{\text{nod}} \to \infty$ ) and  $Z_{\text{Term}} = Z_0$ , it can be shown that the calculations from (5) to (7) results in  $Z_{\text{Tp}} = Z_{\text{Tp}'} = Z_0$ , which agrees with the application of the transmission line theory. Consequently, the impedance seen into the bus from the *p*-th node will be the same for any value of *p* (i.e. independent of the total number of nodes) and equals to  $Z_{\text{bus,p}} = \frac{Z_0}{2}$ .

Computing the voltage attenuation to account for the denominator of the bus transfer function

To compute the attenuation from *p*-th to *q*-th node, given by  $L_{pq}$  in (2), we define the total *T*-matrix for the network in between as

$$T_{\rm tot} = T_{\rm cable} \cdot T_{\rm sec}^{(q-p-1)},\tag{8}$$

in direct correspondence with the elements between p-th and q-th nodes as depicted in Fig. 5. Being  $V_{bus,p}$  and  $V_{bus,q}$  the input and output voltages of this network, respectively, the attenuation can be derived from the T-matrix equations as

$$L_{\rm pq} = \begin{cases} t_{11,\rm tot} + t_{12,\rm tot} \cdot (Y_{\rm nod} + Y_{\rm Tq} \cdot) & \text{if } p < q \\ t_{11,\rm tot} + t_{12,\rm tot} \cdot (Y_{\rm nod} + Y_{\rm Tq}) & \text{if } p > q \end{cases}, \quad (9)$$

taking into account that the output load admittance of the  $T_{\text{tot}}$  network is the parallel of  $Y_{\text{nod}}$  with  $Y_{\text{Tq}'} = Z_{\text{Tq}'}^{-1}$  or  $Y_{\text{Tq}} = Z_{\text{Tq}}^{-1}$  when p < q or p > q, respectively. Finally, the bus transfer function is obtained after replacing (3), (4) and (9) into (2).

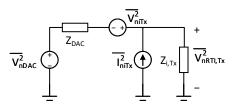

## B. OBTAINING THE RECEIVED NOISE POWER AT AN ARBITRARY NODE POSITION

Concerning the calculation of the received noise power at an arbitrary node, we have to consider the multiple noisy transmitting devices in the system. Hence, we developed the analysis based on the voltage and current noise sources representation in two port networks.

The noise spectral density received by the ADC circuit on each node (cf. Fig. 4) can be computed by considering the total input-referred noise spectral density of the given node  $(\overline{V_n^2}_{\text{RTI}})$  and its voltage gain  $(G_{\text{Rx}})$  as

$$N_{om} = |G_{\rm Rx}|^2 \cdot \overline{V_n^2}_{\rm RTI}.$$

(10)

This total input-referred noise is conformed by the contribution of the following three sources: (i) the noise produced by the receiving amplifier, modeled by its inputreferred voltage and current noise sources,  $\overline{V_{niRx}^2}$  and  $\overline{I_{niRx}^2}$ , respectively [19]; (ii) the output noise current generated by the transmitter amplifier located in the same node, denoted by  $\overline{I_{noTx}^2}$ ; and (iii) the noise voltage received from the bus, denoted by  $\overline{V_n^2}_{\text{bus},q}$ . Analytically, these sources can be combined as

$$\frac{\overline{V_n^2}_{\text{RTI}} = \overline{V_n^2}_{\text{bus},q} + |(Z_{\text{nod}}||Z_{\text{bus},q})|^2 \cdot \left[\frac{\overline{V_{niRx}^2}}{|(Z_{o,\text{Tx}}||Z_{\text{bus},q})|^2} + \overline{I_{niRx}^2} + \overline{I_{noTx}^2}\right] \quad (11)$$

to describe the total noise perceived at the ADC input (cf. Appendix A for derivation).

In the following, we explain the computation of the two noise terms  $\overline{I_{noTx}^2}$  and  $\overline{V_n^2}_{\text{bus,q}}$ , based on the system topology (as shown in Figures 3 and 4) and the circuit element parameters (impedances, admittances and gains). The terms  $\overline{I_{niRx}^2}$  and  $\overline{V_{niRx}^2}$  must be obtained from the datasheet of the amplifier in used.

## 1) Computing the output noise current produced by the transmitter amplifier $(\overline{I_{no\,\text{Tx}}^2})$

To compute the noise current spectral density at the output of the transmitter amplifier (on each node), we consider its input-referred voltage and current noise sources,  $\overline{V_{niT_X}^2}$  and  $\overline{I_{niT_X}^2}$ , respectively [19]. Thus, the short-circuit output noise current delivered by the transconductance amplifier yields

$$\overline{I_{noTx}^2} = |G_m|^2 \cdot \frac{|Z_{i,Tx}|^2}{|Z_{i,Tx} + Z_{DAC}|^2} \cdot (12)$$

$$\cdot \left(\overline{V_{nDAC}^2} + \overline{V_{niTx}^2} + \overline{I_{niTx}^2} \cdot |Z_{DAC}|^2\right),$$

where  $\overline{V_n^2}_{DAC} = 4kTRe\{Z_{DAC}\}$  is the noise spectral density generated by the DAC circuit, *T* is the temperature of the system in kelvins, *k* is the Boltzmann's constant and Re{.} denotes the real part of the impedance [19] (cf. Appendix A for derivation).

For a constant DAC impedance, the addition of the terms containing  $\overline{V_{niTx}^2}$  and  $\overline{I_{niTx}^2}$  can be expressed as a single equivalent noise voltage source, denoted here as  $\overline{V_{neTx}^2}$ , leading to

$$\overline{I_{noTx}^2} = |G_m|^2 \cdot \frac{|Z_{i,Tx}|^2}{|Z_{i,Tx} + Z_{DAC}|^2} \cdot \left(\overline{V_n^2}_{DAC} + \overline{V_{neTx}^2}\right).$$

(13)

2) Computing the noise voltage received from the bus  $(\overline{V_n^2}_{\text{bus,a}})$

The noise voltage received from the bus is produced by all the transmitter amplifiers (excepting for the one located at the given receiving node) and the passive elements in the bus (twisted-pair cable and terminating resistors), affected by the voltage attenuation.

The short-circuit output noise current delivered by each transmitter amplifier  $(\overline{I_{noTx}^2})$  will be analyzed as the mean-square superposition of two different sources. The first source is the thermal noise current that would be generated by the node's output admittance "alone" at the system temperature, computed as  $4kT\operatorname{Re}\{Y_{nod}\}$ . Secondly, we define an excess noise current, denoted by  $\overline{I_{nadd}^2}$ , as the difference

between the real output noise current and the first equivalent source defined above, given by

$$\overline{I_{n\,\text{add}}^{2}} = \overline{I_{no}^{2}}_{\text{Tx}} - 4kT\text{Re}\{Y_{\text{nod}}\}.$$

(14)

Following this approach, the noise voltage from the bus is split into two contributions: (i) the thermal noise produced by the passive elements, including the equivalent thermal noise from nodes' output admittances, denoted by  $\overline{V_n^2}_{\text{nbus},q}^{(\text{pass})}$ ; and (ii) the total contribution from the excess noise current  $(\overline{I_{n\,\text{add}}^2})$  delivered by each transmitter amplifier, denoted by  $\overline{V_n^2}_{\text{nbus},q}^{(\text{add})}$ . This can be expressed as

$$\overline{V_n^2}_{\text{bus},q} = \overline{V_n^2}_{\text{bus},q}^{(\text{pass})} + \overline{V_n^2}_{\text{bus},q}^{(\text{add})}.$$

(15)

The equivalent voltage noise produced by the passive elements (first term in (15)) can be directly obtained as

$$\overline{V_{n \text{ bus},q}^{2(\text{pass})}} = 4kT \text{Re}\{Y_{\text{bus},q}\} \cdot \left| (Z_{\text{nod}} || Z_{\text{bus},q}) \right|^2, \qquad (16)$$

where  $Y_{\text{bus},q}$  represents the equivalent admittance seen into the bus from q-th node.

Regarding the excess noise, we superpose the contribution of all the sources from the left and right side of the q-th node as follows

$$\overline{V_n^2}_{\text{bus},q}^{(\text{add})} = \sum_{\substack{k=1\\k \neq q}}^M \frac{\overline{V_n^2}_k^{(\text{add})}}{|L_{\text{kq}}|^2},$$

(17)

where  $L_{kq}$  is the voltage attenuation computed as in (9), and  $\overline{V_n^2}_k^{(add)}$  is the noise voltage produced, on a remote *k*-th node, by the excess noise current located in that same node, and given by

$$\overline{V_n^2}_k^{(\mathrm{add})} = \overline{I_n^2}_{\mathrm{add}} \cdot \left| \left( Z_{\mathrm{nod}} || Z_{\mathrm{bus},k} \right) \right|^2.$$

(18)

Finally, by replacing (14) in (18), and the resulting operation into (17), we obtain the second term in  $\overline{V_n^2}_{h \text{ bus,a}}$ .

#### V. CASE STUDY

In this section, we validate the proposed SNR computation methodology by comparing its results with those obtained by the circuit simulator PathWave RF Synthesis (Genesys)<sup>1</sup>. As a case of study, different numbers of nodes (up to five) are connected through a bus topology, as illustrated in the circuit schematic in Fig. 6 a) for the three-nodes case. We have considered the characteristics of commercially available integrated circuits for the implementation of the system: AD9234 for the ADC, AD9735 for the DAC, AD8375 for the transmitter amplifier, and AD8351 for the receiver amplifier. The main criteria to select these amplifier circuits were their differential output (for the transmitter) or input (for the receiver) interfaces and their respective high impedance values. The cable is the typically reported Cat5 unshielded twisted-pair (UTP).

<sup>&</sup>lt;sup>1</sup>This is a product of Keysight Technologies company.

### A. MODELING

#### 1) Circuit Simulator Model

To illustrate the agreement of the derived formulations, the circuit schematic depicted in Fig. 6a simulates the point-to-point communication from the first to the third node, in a three-nodes bus. The *i*-th node includes the subcircuits Gmi and Avi, which model the transmitter and receiver amplifiers, respectively. These subcircuit models are shown in Fig. 6 b) and c), and later discussed in this section.

The transmitted signal is generated by a source (PORT=1) with the same output impedance as the DAC, which is connected to the transmitter amplifier. The received signal is measured by a load (PORT=2) with the same impedance as the ADC, which is connected to the receiver amplifier. Resistors are used to model the load effect of DAC and ADC devices, in the idle amplifiers, as well as the terminators on the line. Ports and resistors models include noise generation.

The twisted-pair cable connecting each node is modeled by introducing its impedance matrix in the simulator, using a software's built-in function for 2-port network analysis. The Z-parameters are obtained by the transformation of the T-matrix calculated as indicated in (6). The characteristic impedance and the propagation factor of the twisted-pair cable are computed by the so-called KHM model [9], as

$$Z_0 = (h_1 + h_2 f^{-\frac{1}{2}}) - ih_2 f^{-\frac{1}{2}}$$

(19)

$$\gamma = (k_1 \sqrt{f} + k_2 f) + i(k_1 \sqrt{f} - k_2 \frac{2}{\pi} f \ln f + k_3),$$

where  $h_1$ ,  $h_2$ ,  $k_1$ ,  $k_2$ , and  $k_3$  are cable parameters, given in [9].

The transmitter and receiver amplifiers are modeled as depicted in Fig. 6 b) and c), respectively, according to the specifications obtained from their datasheets. Both schematics consist of the devices' internal models (elements inside the dashed-line boxes), and external passive elements recommended by the manufacturer.

The transmitter amplifier (cf. Fig. 6 b), is modelled by a voltage-controlled current source (VCCS), defined in the software by the following parameters: the transconductance T, the input resistance RI, and the output resistance RO. The output impedance of the amplifying device is completed by the capacitor C1. The noise source (VNOISE) models the equivalent input noise voltage,  $\overline{V_{neTx}^2}$ , for a  $150 \Omega$  source, which is the same impedance presented by the DAC circuit. L1 and L2 simulate radiofrequency inductors, required to bias the transmitter amplifier's output. They use the simulation model of the hardware device Coilcraft 0805LS-332, provided by its manufacturer, which includes frequency-dependent parasitic effects and noise.

The receiver amplifier model (cf. Fig. 6 c) consists of a voltage-controlled voltage source (VCVS) with voltage gain MU, input resistance RIN, and the output resistance ROUT. Capacitors C1 and C2 account for the reactive part of the input and output impedances, respectively. Sources VNOISE and INOISE will model the input-referred voltage

Figure 6: Simulation schematics: a) three-nodes bus, first node transmitting and third node receiving; b) transmitter amplifier; and c) receiver amplifier.

and current noises, respectively. The noise of the matching resistor R1 is included in the simulation.

Regarding the AD8351 noise model, only the combined effect of the input-referred voltage and current noises, accounting for a connected 50  $\Omega$  source, is given by the manufacturer, denoted here as  $\overline{V_{neRx}^2}$ . To overcome this limitation, we simulated the two extreme cases, namely: (i) all the noise is produced by the voltage source (i.e.,  $\overline{V_{niRx}^2} = \overline{V_{neRx}^2}$ ;  $\overline{I_{niRx}^2} = 0$ ), which yields the worst case scenario when the source impedances are lower than 50  $\Omega$ ; and (ii) all the noise is produced by the current source (i.e.,  $\overline{V_{niRx}^2} = 0$ ;  $\overline{I_{niRx}^2} = \frac{\overline{V_{neRx}^2}}{|50 \Omega|^2}$ ), which yields the worst case scenario when the source impedances are higher than 50  $\Omega$ . After running both simulations, the highest value of the output noise is the one used in the analysis.

#### 2) Analytical model parameters

The above models were translated to the terms required for the analytical calculations (equations derived in Section IV), by means of circuit analysis techniques (namely Thevenin and Norton Theorems). Particularly, to account for the worst-case analysis, concerning the input-referred noise in

## IEEE Access

the receiver amplifier, the expression (11) was rewritten as

$$\overline{V_{n\,\text{RTI}}^{2}} = \overline{V_{n\,\text{bus},q}^{2}} + |(Z_{\text{nod}}||Z_{\text{bus},q})|^{2} \cdot$$

$$\cdot \left\{ \max\left[ \frac{\overline{V_{ne}^{2}}_{\text{Rx}}}{|(Z_{o,\text{Tx}}||Z_{\text{bus},q})|^{2}}, \frac{\overline{V_{ne}^{2}}_{\text{Rx}}}{|50\ \Omega|^{2}} \right] + \overline{I_{no}^{2}}_{\text{Tx}} \right\}.$$

(20)

Finally, the parameters employed to model the system (including the transmitted OFDM waveform) are summarized in Table 2.

Table 2: Summary of parameters regarding the OFDM waveform and the circuit elements<sup>a</sup>.

| Parameter                                  | Value                                                               | Parameter                                | Value                                |  |  |  |  |

|--------------------------------------------|---------------------------------------------------------------------|------------------------------------------|--------------------------------------|--|--|--|--|

| $\Delta f$                                 | 24.41 kHz                                                           | T                                        | 300 K                                |  |  |  |  |

| $G_m$                                      | 67 mS                                                               | $A_v$                                    | 20                                   |  |  |  |  |

| $Z_{i,Tx}$                                 | $150\Omega$                                                         | $Z_{i,Rx}$                               | $5\mathrm{k}\Omega  0.8\mathrm{pF}$  |  |  |  |  |

| $Z_{o,Tx}$                                 | $5.3\mathrm{k}\Omega  6.8\mathrm{\mu H}$                            | $Z_{o,Rx}$                               | $200\Omega  0.45\mathrm{pF}$         |  |  |  |  |

| $\sqrt{\overline{V_{ne}^2}}_{\mathrm{Tx}}$ | $3.57\mathrm{nV}/\sqrt{\mathrm{Hz}}$                                | $\sqrt{\overline{V_{ne}^2}}_{\text{Rx}}$ | $2.65\mathrm{nV}/\sqrt{\mathrm{Hz}}$ |  |  |  |  |

| $Z_{\rm DAC}$                              | $150\Omega$                                                         | $Z_{ADC}$                                | $100 \Omega$                         |  |  |  |  |

| NFFT                                       | 256, 512, 1024, 2048                                                |                                          |                                      |  |  |  |  |

| Cable parameters                           | Cable parameters $h_1 = 101.2393, h_2 = 3.2608 \cdot 10^3,$         |                                          |                                      |  |  |  |  |

| (KHM model)                                | KHM model) $k_1 = 2.07 \cdot 10^{-3}, k_2 = 2.39281 \cdot 10^{-8},$ |                                          |                                      |  |  |  |  |

|                                            | $k_3 = 2.94153 \cdot 10^{-5}$                                       |                                          |                                      |  |  |  |  |

<sup>*a*</sup>In this table, values for frequency-dependent equivalent parameters are calculated at 7.2 MHz. However, the analysis were conducted considering their actual dependency with frequency.

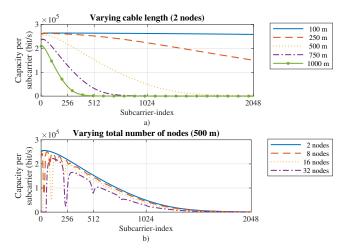

### B. VALIDATION OF THE CALCULATION METHODOLOGY

Three different experiments were conducted to validate the calculation methodology, regarding the cable length, the total number of connected nodes, and the location of the transmitter-receiver nodes pair in the bus. Firstly, the cable length was varied in a two-node bus. Secondly, for a fixed distance between the two ends of the bus (500 m), the transmission from the first to the last node was evaluated with a different number of nodes in between. Finally, in a five-node bus with a total length of 500 m, the first node was set as the transmitter and the location of the receiver was shifted. The analyzed frequency range corresponds to the OFDM parameters in Table 2, where the subcarrier index is related to the linear frequency as  $f_m = m \cdot \Delta f + f_o$ , and  $f_o$ represents the offset frequency to transmit a band-pass signal through the channel. Following this relation, the frequency range will be given by  $\left[f_o; \text{NFFT} \cdot \Delta f + \frac{\Delta f}{2} + f_o\right]$ , where we have considered  $f_o = 1 \text{ MHz}$  and the largest OFDM symbol as NFFT = 2048.

The system performance was evaluated through the noise figure, denoted as NF. According to its definition [19], the noise figure includes both the voltage transfer function and the output noise spectral density as

$$NF = 10 \log \left( \frac{N_{om}}{4kT_0 \operatorname{Re}\{Z_{\mathrm{DAC}}\} |H|^2} \right), \qquad (21)$$

Figure 7: Validation of the proposed SNR computation methodology: a) varying the cable length in a two-nodes bus; b) end-to-end communication varying the total number of nodes with fixed total bus length of 500 m; and c) varying the receiving-node location in a five-nodes bus with a fixed total length of 500 m.

where  $T_0 = 290$  K, and the dependency of the terms with f was omitted for brevity.

The comparison between the proposed theoretical formulation and the circuit simulation is depicted in Fig. 7 accounting for different cable lengths in a), the total of nodes in b), and the location of the receiver node in c). The results regarding these three different sets of curves exhibit absolute agreement between the proposed analytical methodology and the circuit simulation, including the oscillatory behavior observed for low frequencies (caused by loading effects due to undesirable impedance mismatching).

#### **VI. RESULTS AND DISCUSSION**

Results and discussion are presented regarding the impact of the cable length and the total number of nodes on the achievable channel capacity. We evaluate the channel capacity per subcarrier considering the use of G.hn OFDM waveform parameters, as indicated in Table 2, with nodes equidistantly located on the bus.

For a more realistic scenario when analyzing the channel

Figure 8: Achievable channel capacity. a) Impact of the length of the cable for the connection in between two nodes. b) Impact of the total number of nodes for the cable length of 500 m.

capacity, we consider the SNR gap approximation to account for a predefined symbol error rate (SER) in additive white Gaussian noise (AWGN) channels [36]. We compute this metric per subcarrier as  $C_m = \log_2 \left(1 + \frac{1}{\Gamma} \text{SNR}_m\right)$  by considering the impact of errors on the  $\Gamma$  factor, where SNR<sub>m</sub> is computed based on the proposed methodology in Section IV, and the circuit and OFDM parameters as presented in Section V (cf. Table 2). The  $\Gamma$  factor will be given by  $\Gamma = \frac{1}{3} \left[ Q^{-1} \left( \frac{\text{SER}}{4} \right) \right]$  according to the conforming of M-QAM waveforms per subcarrier index [37], where we assume a predefined SER =  $10^{-5}$  for the QAM transmitted modulation.

To illustrate the behavior of the achieved capacity per subcarrier versus the cable length only, Fig. 8 a) depicts the case for a varying distance between two nodes, while Fig. 8 b) depicts the case for a varying total number of connected nodes on a cable of 500 m total length. Based on the results in Fig. 8 a), the capacity per subcarrier  $(C_m)$  will be highly reduced with the increasing of the cable length. For instance, this will imply that up to 250 meters a 2048-FFT symbol size can be used to transmit information, and after 500 m the FFT size can not be larger than 1024. Considering the results in Fig. 8 b), the impact of the total number of nodes is not so significant, consistent with the model validation results (cf. Fig. 7 b)). Regarding the 500 m cable, increasing the total number of nodes does not cause a reduction in the FFT size (1024 in this case). This behaviour has been observed for several cable lengths.

The periodic local minima perceived in the channel capacity at lower subcarrier-indexes (cf. Fig. 8 b) are caused by the low-frequency oscillatory behaviour of the voltage transfer function and the noise, presented in Fig. 7. It arises at lower frequencies where the effects of the output inductors' impedance are noticeable. This phenomenon coincide with local extrema occurring in the imaginary part of the

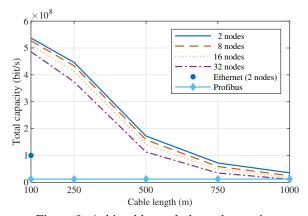

Figure 9: Achievable total channel capacity.

equivalent impedance of the bus, when the length of the cable between nodes is a multiple of half of the transmitted carrier wavelength [30]. However, even when actions to reduce low-frequency mismatches could be considered in the circuit implementation in a future work, bit loading functionalities implemented over the OFDM waveforms may be used to avoid the impact of this oscillatory frequency band.

Finally, Fig. 9 depicts the total channel capacity, considering all the OFDM subcarriers, by varying the cable length and the total number of nodes. Results exhibit that the channel capacity ranges from a maximum of 512 Mbit/s (100 m cable, 2 nodes) and a minimum of 11 Mbit/s (1 km cable, 32 nodes). As depicted in Fig. 9, in contrast to the Ethernet-based solutions ( $\sim 100 \text{ Mbit/s}$ ) and fieldbuses  $(\sim 12 \text{ Mbit/s})$ , our proposal overcomes both systems, exhibiting an increased bandwidth for extended distances between nodes. That is, when compared to Ethernet at 100 m distance, the achievable capacity is five times larger, but moreover, our proposal can go beyond this distance in contrast to Ethernet solution. Then, when compared to the fieldbuses, the presented solution achieves a much larger capacity, in the order of fifty times for 100 m distance and more than ten times for 0.5 km. We also remark the similar performance to fieldbuses in the worst condition scenario, i.e., along 1 km cable length with 32 connected nodes. This result demonstrates the realistic behavior of the presented proposal.

#### **VII. CONCLUSIONS**

Although the variety of reported solutions exhibit acceptable performance, further improvements can be achieved with the transmission of multicarrier waveforms in wired industrial networks. In this direction, the current proposal has addressed the use of OFDM waveforms to implement the fieldbuses topologies. By means of the discussed circuit bus-topology, the achievable capacity exhibits higher values over larger distances when compared to similarly reported fieldbuses and Ethernet-based networks. Besides, considering the flexible numerology of OFDM waveforms, further

Figure 10: Noise sources at the input of the receiving amplifier.

counteracting mechanisms to the ruggedness of industrial environments can be implemented. In this regard, future work will be conducted to analyze and conceive resource allocation mechanisms to account for the particularities of industrial applications, where deterministic behaviors and higher transmission speeds are demanded features in high interference environments. We also aim to further analyze OFDM transmission on fieldbuses by conceiving its implementation in hardware.

## APPENDIX A EQUIVALENT CIRCUITS FOR THE NOISE CALCULATION IN THE AMPLIFIERS

The expression for the total input-referred noise spectral density  $(V_{n \text{ RTI}}^2)$ , regarding the receiving amplifier in the q-th node, is obtained from the equivalent circuit depicted in Fig. 10. The input-referred voltage and current noise sources, denoted by  $\overline{V_{ni_{Rx}}^2}$  and  $\overline{I_{ni_{Rx}}^2}$ , respectively, model the noise produced internally by the receiving amplifier [19]. The current source  $\overline{I_{no}^2}_{T_x}$  accounts for the output noise generated by the transmitter amplifier located in the same node. Finally, the current source  $\overline{I_{n\,\text{bus},q}^2}$  models the total noise generated in the bus, as perceived in the q-th node. From this circuit, we find the value of  $V_{n \text{ RTI}}^2$  as the superposition of the effect of each noise source separately. Particularly, we refer to the contribution from the source  $I_{n \text{ bus},q}^2$  as the noise voltage received from the bus and denoted as  $\overline{V_n^2}_{\text{bus,q}}$ . The contributions from other sources are found by applying basic circuit analysis techniques. The result is given in (11), provided in Section IV-B.

The short-circuit output noise current  $(\overline{I_{noTx}^2})$ , regarding the transmitter amplifier is given by

$$\overline{I_{no}^2}_{Tx} = |G_m|^2 \cdot \overline{V_n^2}_{RTI,Tx},$$

(22)

where  $\overline{V_n^2}_{RTI,Tx}$  is the total input-referred noise spectral density, produced by the noise sources in the equivalent circuit represented in Fig. 11. The input-referred voltage and current noise sources, denoted by  $\overline{V_{niTx}^2}$  and  $\overline{I_{niTx}^2}$ , respectively, model the noise produced by the transmitter amplifier itself [19]. The source  $\overline{V_n^2}_{DAC}$  is the noise spectral density generated by the DAC circuit.

The value for  $\overline{V_{n \text{ RTI,Tx}}^2}$  is obtained by the superposition VOLUME 9, 2016

Figure 11: Noise sources at the input of the transmitter amplifier.

of the noise sources as

$$\overline{V_n^2}_{\text{RTI,Tx}} = \frac{|Z_{i,\text{Tx}}|^2}{|Z_{i,\text{Tx}} + Z_{\text{DAC}}|^2} \cdot \left(\overline{V_n^2}_{\text{DAC}} + \overline{V_{ni}^2}_{\text{Tx}} + \overline{I_{ni}^2}_{\text{Tx}} \cdot |Z_{\text{DAC}}|^2\right)$$

(23)

Finally, replacing (23) in (22) yields (12), provided in Section IV-B.

#### References

- M. Wollschlaeger, T. Sauter, and J. Jasperneite, "The Future of Industrial Communication: Automation Networks in the Era of the Internet of Things and Industry 4.0," *IEEE Industrial Electronics Magazine*, vol. 11, no. 1, pp. 1932–4529, Mar. 2017.

- [2] B. Chen, J. Wan, L. Shu, P. Li, M. Mukherjee, and B. Yin, "Smart factory of industry 4.0: Key technologies, application case, and challenges," *IEEE Access*, vol. 6, pp. 6505–6519, 2018.

- [3] H. Kagermann, W.-D. Lukas, and W. Wahlster, "Industrie 4.0: Mit dem Internet der Dinge auf dem Weg zur 4. industriellen Revolution," ingenieur.de, White Paper, Apr. 2011. [Online]. Available: https://www.ingenieur.de/technik/fachbereiche/produktion/ industrie-40-mit-internet-dinge-weg-4-industriellen-revolution/

- [4] K. Zhou, T. Liu, and L. Zhou, "Industry 4.0: Towards future industrial opportunities and challenges," in 2015 12th International Conference on Fuzzy Systems and Knowledge Discovery (FSKD). Zhangjiajie, China: IEEE, Aug. 2015.

- [5] G. Aceto, V. Persico, and A. Pescape, "A Survey on Information and Communication Technologies for Industry 4.0: State-of-the-Art, Taxonomies, Perspectives, and Challenges," *IEEE Communications Surveys & Tutorials*, vol. 21, no. 4, pp. 3467–3501, 2019.

- [6] T. Sauter, "The continuing evolution of integration in manufacturing automation," *IEEE Industrial Electronics Magazine*, vol. 1, no. 1, pp. 10– 19, 2007.

- [7] J. Montalban, E. Iradier, P. Angueira, O. Seijo, and I. Val, "Noma-based 802.11n for industrial automation," *IEEE Access*, vol. 8, pp. 168546– 168557, 2020.

- [8] M. Gundall, M. Strufe, H. D. Schotten, P. Rost, C. Markwart, R. Blunk, A. Neumann, J. Grießbach, M. Aleksy, and D. Wübben, "Introduction of a 5g-enabled architecture for the realization of industry 4.0 use cases," *IEEE Access*, vol. 9, pp. 25 508–25 521, 2021.

- [9] D. Acatauassu, S. Host, C. Lu, M. Berg, A. Klautau, and P. O. Borjesson, "Simple and Causal Copper Cable Model Suitable for G.fast Frequencies," *IEEE Transactions on Communications*, vol. 62, no. 11, pp. 4040–4051, Nov. 2014.

- [10] R. Zurawski, Ed., *The Industrial Information Technology Handbook*, ser. Industrial Electronics Series. Boca Raton, FL: CRC Press, 2004.

- [11] M. Felser, "Real-Time Ethernet Industry Prospective," *Proceedings of the IEEE*, vol. 93, no. 6, pp. 1118–1129, Jun. 2005.

- [12] L. Lo Bello and W. Steiner, "A Perspective on IEEE Time-Sensitive Networking for Industrial Communication and Automation Systems," *Proceedings of the IEEE*, vol. 107, no. 6, pp. 1094–1120, Jun. 2019.

- [13] P. Pinceti, "Fieldbus: more than a communication link," *IEEE Instrumen*tation & Measurement Magazine, vol. 7, no. 1, pp. 17–23, Mar. 2004.

- [14] Y. George and O. Amrani, "Bit loading algorithms for OFDM," in *International Symposium on Information Theory*, 2004 (ISIT 2004). Chicago, IL: IEEE, Jan. 2005.

- [15] Y. Cui, V. K. N. Lau, R. Wang, H. Huang, and S. Zhang, "A Survey on Delay-Aware Resource Control for Wireless Systems—Large Deviation Theory, Stochastic Lyapunov Drift, and Distributed Stochastic Learning,"

11

IEEE Transactions on Information Theory, vol. 58, no. 3, pp. 1677–1701, Mar. 2012.

- [16] "Network and Customer Installation Interfaces—Asymmetric Digital Subscriber Line (ADSL) Metallic Interface," ANSI, Std ANSI T1.413, Aug. 1995.

- [17] V. Oksman and S. Galli, "G.hn: The new ITU-T home networking standard," *IEEE Communications Standards Magazine*, vol. 47, no. 10, pp. 138–145, 2009.

- [18] A. M. Tonello, S. D'Alessandro, and L. Lampe, "Cyclic Prefix Design and Allocation in Bit-Loaded OFDM over Power Line Communication Channels," *IEEE Transactions on Communications*, vol. 58, no. 11, pp. 3265–3276, Nov. 2010.

- [19] B. Razavi, Design of Analog CMOS Integrated Circuits, 2nd ed. McGraw-Hill, 2017.

- [20] J. Randa, "Noise characterization of multiport amplifiers," *IEEE Transac*tions on Microwave Theory and Techniques, vol. 49, no. 10, pp. 1757– 1763, 2001.

- [21] L. Moura, P. P. Monteiro, and I. Darwazeh, "Generalized noise analysis technique for four-port linear networks," *IEEE Transactions on Circuits* and Systems I: Regular Papers, vol. 52, no. 3, pp. 631–640, 2005.

- [22] M. T. Ivrlač and J. A. Nossek, "Toward a circuit theory of communication," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 57, no. 7, pp. 1663–1683, 2010.

- [23] R. Sinha, "Design of multi-port with desired reference impedances using y-matrix and matching networks," *IEEE Transactions on Circuits and Systems I: Regular Papers*, pp. 1–11, 2021.

- [24] "IEC 61158-2: Digital data communications for measurement and control - Fieldbus for use in industrial control systems - Part 2: Physical layer specification and service definition," IEC, Std IEC 61158-2:2003, May 2003.

- [25] "Industrial communication networks Profiles Part 1: Fieldbus profiles," IEC, Std IEC61784-1:2019, Apr. 2019.

- [26] "Industrial communication networks Profiles Part 2: Additional fieldbus profiles for real-time networks based on ISO/IEC/IEEE 8802-3," IEC, Std IEC61784-2:2019, Apr. 2019.

- [27] J.-d. Decotignie, "The Many Faces of Industrial Ethernet [Past and Present]," *IEEE Industrial Electronics Magazine*, vol. 3, no. 1, pp. 8–19, Mar. 2009.

- [28] Y. Li, J. Jiang, C. Lee, and S. H. Hong, "Practical implementation of an opc ua tsn communication architecture for a manufacturing system," *IEEE Access*, vol. 8, pp. 200 100–200 111, 2020.

- [29] Z. E. Ankarali, B. Pekoz, and H. Arslan, "Flexible Radio Access Beyond 5G: A Future Projection on Waveform, Numerology, and Frame Design Principles," *IEEE Access*, vol. 5, pp. 18 295–18 309, Jun. 2017.

- [30] D. M. Pozar, Microwave engineering, 4th ed. Wiley, 2012.

- [31] H. Rohling, Ed., OFDM: Concepts for Future Communication Systems, ser. Signals and Communication Technology. Springer, 2011.

- [32] A. B. Carlson, P. B. Crilly, and J. C. Rutledge, Communication Systems: An Introduction to Signals and Noise in Electrical Communication, 4th ed. McGraw-Hill, 2002.

- [33] A. V. Oppenheim and R. W. Schafer, Discrete-Time Signal Processing: Pearson New International Edition, 3rd ed. Harlow, United Kingdom: Pearson Education Limited, 2013.

- [34] N. Lingampelly, "Bit Error Rate of Twisted Pair Cable for Different Noise Environments a Novel Approach," *International Journal of Emerging Trends in Science and Technology (IJETST)*, vol. 3, no. 12, Dec. 2016.

- [35] W. Hayt, J. Kemmerly, J. Phillips, and S. Durbin, *Engineering Circuit Analysis*, 9th ed. New York City, NY: McGraw-Hill Education, 2019.

- [36] A. Garcia-Armada, "SNR gap approximation for M-PSK-Based bit loading," *IEEE Transactions on Wireless Communications (TWC)*, vol. 5, no. 1, pp. 57–60, Jan. 2006.

- [37] J. Cioffi, G. Dudevoir, M. Eyuboglu, and G. Forney, "MMSE decision-feedback equalizers and coding. II. Coding results," *IEEE Transactions on Communications*, vol. 43, no. 10, pp. 2595–2604, 1995.

JORGE LUIS GONZÁLEZ RIOS is with the Interdisciplinary Centre for Security, Reliability and Trust (SnT), University of Luxembourg. He received his B.S. Degree (with honors), M.S. Degree and Ph.D. on Telecommunications and Electronics in 2006, 2009 and 2018, respectively, from the Technological University of Havana (CUJAE), Cuba. From September 2006 to July 2019 he was as Lecturer and Researcher with the Research Center on Microelectronics (CIME) at

CUJAE. He visited the Seville Institute of Microelectronics (IMSE-CNM), Spain, in 2010, 2011 and 2012, and the Group of Microelectronics of the Federal University of Itajuba (UNIFEI), Brazil, in 2013. His research interests include RF/analog circuits, embedded systems and wireless and satellite communications.

JORGE TORRES GÓMEZ received the B.Sc. (2008), M.Sc. (2010), and Ph.D. (2015) degrees from the Havana University of Technology, CU-JAE, Cuba. He is currently with the School of Electrical Engineering and Computer Science, TU Berlin. From 2008 to 2018, he lectured with the School of Telecommunications and Electronics, CUJAE. He has been with the Department of Signal Theory and Communications, UC3M, Spain, as a guest lecturer, and with the TU Chemnitz as

a postdoc. He is with the committee of Teaching and Professional Activities in the IEEE German Chapter, Executive Committee. He is member of the Cuban association of pattern recognition (ACRP). His research interests include DSP, SDR, and Education. He has been participating in DAAD, Erasmus+ and CAPES research projects. He is reviewer of Physical Communication, RIELAC and Telematic journals, as well as Vehicular Technology Conference (VTC).

RAJESH KUMAR SHARMA (S'07-M'11) is with the Department of Digital Signal Processing and Circuit Technology, Chemnitz University of Technology, Germany. He received the B.Sc. degree (with honors) in electrical engineering from the University of Engineering and Technology, Lahore, Pakistan, in 1998, the M. Eng. degree in telecommunications from the Asian Institute of Technology (AIT), Pathumthani, Thailand, in 2002, and the Ph.D. degree in electrical engineer-

ing from Jacobs University, Bremen, Germany, in 2010. He has occupied several academic positions as lecturer in the Department of Electrical and Electronics Engineering, Kathmandu University, Dhulikhel, Nepal, postdoctoral researcher at Jacobs University, Germany, and as a researcher with the Cognitive Radio Network Group (CRNG) in the International Graduate School on Mobile Communications, Ilmenau University of Technology, Ilmenau, Germany. His current research focus is on cognitive radio, wireless physical-layer security, Multicarrier communications, wireless channel modeling, and 5G technologies.

FALKO DRESSLER is full professor and Chair for Data Communications and Networking at the School of Electrical Engineering and Computer Science, TU Berlin. He received his M.Sc. and Ph.D. degrees from the Dept. of Computer Science, University of Erlangen in 1998 and 2003, respectively. Dr. Dressler has been associate editor-in-chief for IEEE Trans. on Mobile Computing and Elsevier Computer Communications as well as an editor for journals such as

IEEE/ACM Trans. on Networking, IEEE Trans. on Network Science and Engineering, Elsevier Ad Hoc Networks, and Elsevier Nano Communication Networks. He has been chairing conferences such as IEEE INFOCOM, ACM MobiSys, ACM MobiHoc, IEEE VNC, IEEE GLOBECOM. He authored the textbooks Self-Organization in Sensor and Actor Networks published by Wiley & Sons and Vehicular Networking published by Cambridge University Press. He has been an IEEE Distinguished Lecturer as well as an ACM Distinguished Speaker. Dr. Dressler is an IEEE Fellow as well as an ACM Distinguished Member. He is a member of the German National Academy of Science and Engineering (acatech). He has been serving on the IEEE COMSOC Conference Council and the ACM SIGMOBILE Executive Committee. His research objectives include adaptive wireless networking (sub-6GHz, mmWave, visible light, molecular communication) and wireless-based sensing with applications in ad hoc and sensor networks, the Internet of Things, and Cyber-Physical Systems.

M. JULIA FERNÁNDEZ-GETINO GARCÍA (S'99 - AM'02 - M'03) received the M. Eng. and Ph.D. degrees in telecommunication engineering from the Polytechnic University of Madrid, Spain, in 1996 and 2001, respectively. She is currently with the Department of Signal Theory and Communications, Carlos III University of Madrid, Spain, as an Associate Professor. From 1996 to 2001, she held a research position with the Department of Signals, Systems and Radiocommu-

nications, Polytechnic University of Madrid. She visited Bell Laboratories, Murray Hill, NJ, USA, in 1998; visited Lund University, Sweden, during two periods in 1999 and 2000; visited Politecnico di Torino, Italy, in 2003 and 2004; and visited Aveiro University, Portugal, in 2009 and 2010. Her research interests include multicarrier communications, coding and signal processing for wireless systems.

She received the best "Master Thesis" and "Ph.D. Thesis" awards from the Professional Association of Telecommunication Engineers of Spain in 1998 and 2003, respectively; the "Student Paper Award" at the IEEE International Symposium on Personal, Indoor and Mobile Radio Communications (PIMRC) in 1999; the "Certificate of Appreciation" at the IEEE Vehicular Technology Conference (VTC) in 2000; the "Ph.D. Extraordinary Award" from the Polytechnic University of Madrid in 2004; the "Juan de la Cierva National Award" from AENA Foundation in 2004; and the "Excellence Award" from Carlos III University of Madrid in 2012 for her research career.